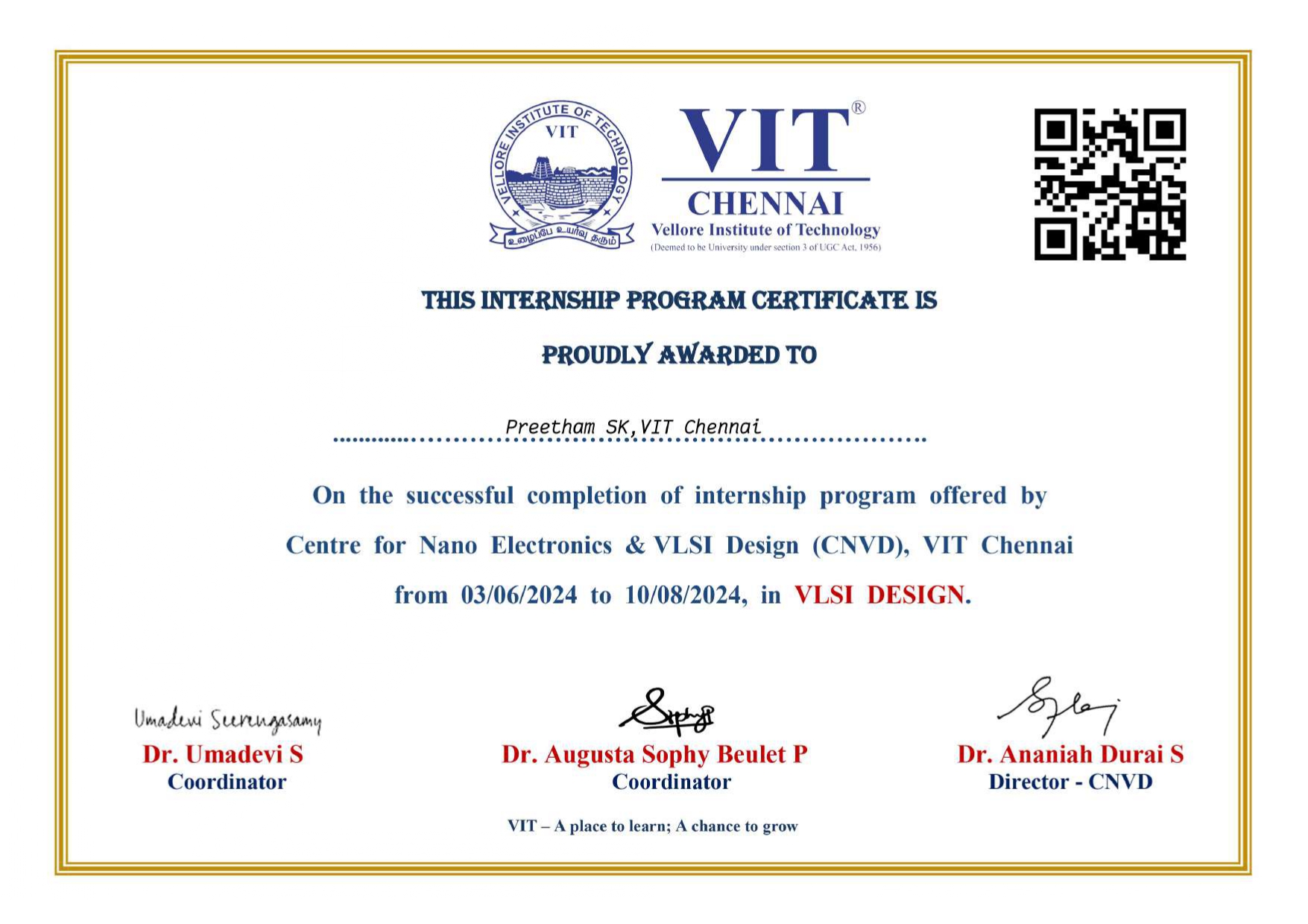

Center for Nano Electronics & VLSI Design (CNVD)

Summer Research Intern

Jun 2024 – Aug 2024

MAC UNIT

Designed a 16×16 Multiply-Accumulate (MAC) unit in Verilog HDL using Row Bypass Adder (RBA) scheme — reducing switching activity and dynamic power compared to conventional ripple carry adder based designs.

SIMULATION

Functionally verified using Cadence® NC Launch; gate-level synthesis performed using Cadence® Genus with standard cell library mapping.

OUTCOME — MAC unit architecture inspired innovation in reconfigurable binary multiplier design; resulted in Indian Patent Application No. 202541080342, published September 2025.

HOVER / CLICK TO VIEW CERTIFICATE