SYMPOSIUM — SEP 2024

VDAT 2024 — International Symposium on VLSI Design and Test

28th Edition · VIT Vellore · Attendee

SEP 2024

EVENT

Attended the 28th International Symposium on VLSI Design and Test held at VIT Vellore — one of India's premier academic forums on VLSI chip design, test methodologies, verification, and semiconductor research.

EXPOSURE

Engaged with cutting-edge research presentations, industry sessions on EDA tools, and academic talks covering physical design, low-power techniques, and advanced test strategies — directly relevant to graduate-level VLSI research.

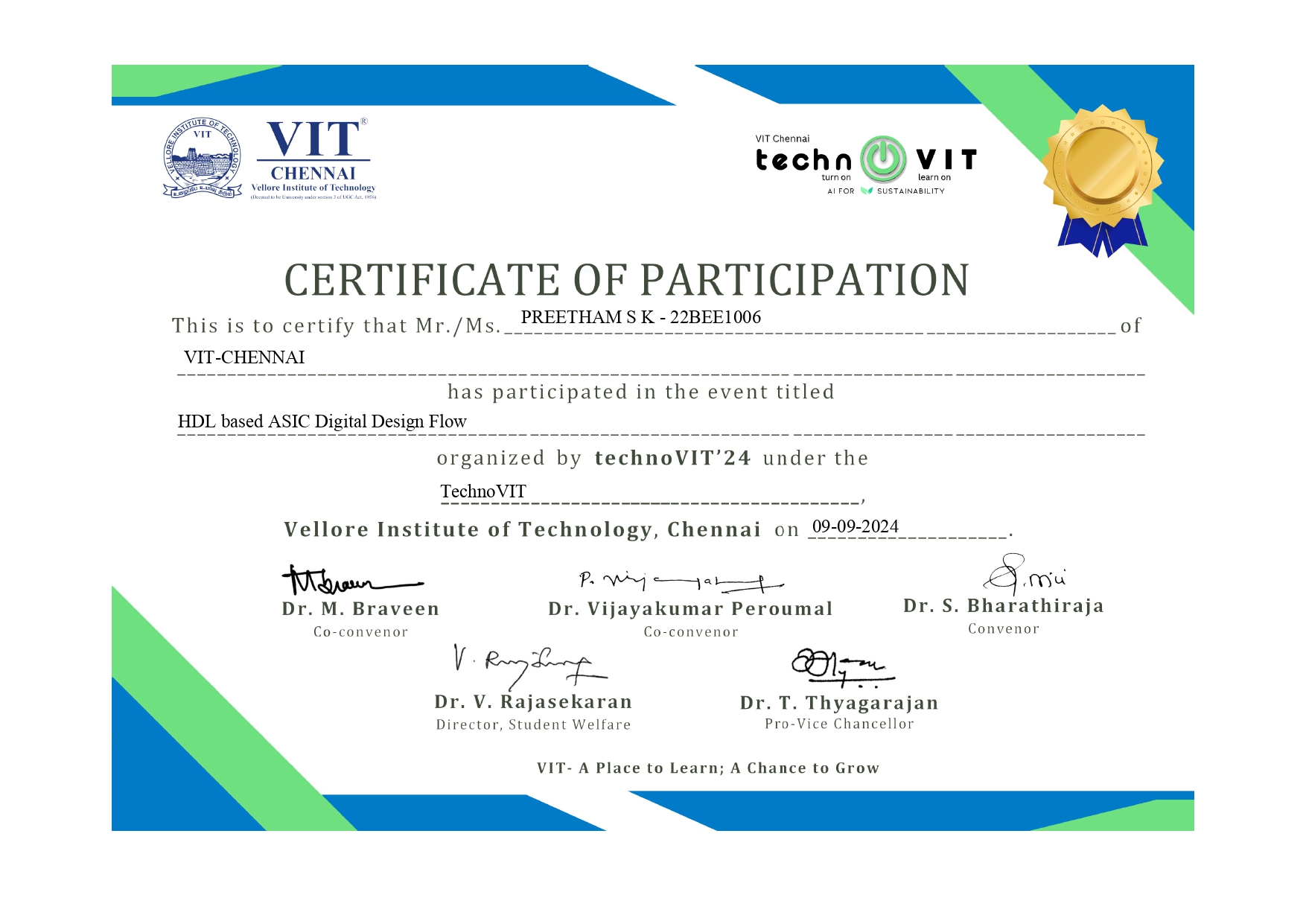

HOVER TO VIEW CERTIFICATE