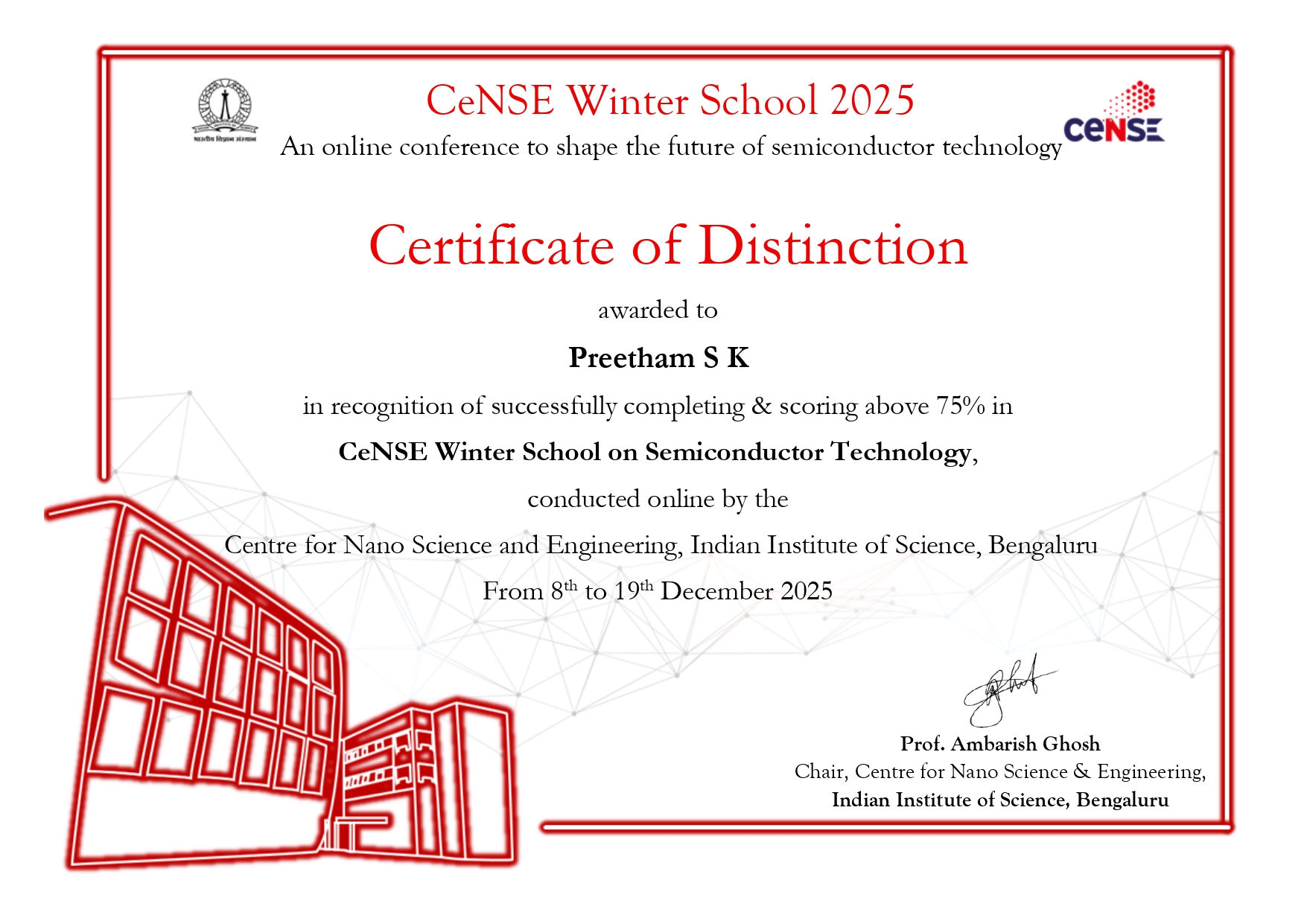

INSTITUTE PROGRAMME

Centre for Nano Science and Engineering, IISc Bengaluru

⭐ CERTIFICATE OF DISTINCTION

CeNSE Winter School on Semiconductor Technology

Centre for Nano Science and Engineering, IISc Bengaluru

DEC 2025

PROGRAMME SCOPE

An intensive two-week online conference-cum-school organised by IISc's Centre for Nano Science and Engineering, focused on shaping the future of semiconductor technology — covering device physics, nanofabrication, CMOS scaling, and advanced materials.

TOPICS COVERED

Semiconductor device fundamentals · MOSFET scaling and short-channel effects · Nanofabrication techniques · CMOS circuit design · Emerging semiconductor materials · Photonics and optoelectronics · IC packaging and reliability.

ACHIEVEMENT

Awarded Certificate of Distinction — scored above 75% in the programme assessment. Signed by Prof. Ambarish Ghosh, Chair, CeNSE, IISc Bengaluru.

OUTCOME — Recognition of distinction-level performance in a nationally competitive semiconductor school conducted by one of India's premier research institutes. Deepened understanding of device-level semiconductor physics relevant to VLSI design.

HOVER TO VIEW CERTIFICATE